仅用于站内搜索,没有排版格式,具体信息请跳转上方微信公众号内链接

以下文章来源于微信公众号:车规半导体硬件

作者:ZOMI酱

链接:https ://mp.weixin.qq.com/s/hCmqaLSnC5rZDXE_f8lQuQ

本文仅用于学术分享,如有侵权,请联系后台作删文处理

导读

GPU因其强大的并行计算能力,在AI计算中占据核心地位。本文从GPU与CPU在架构和执行模式上的本质差异出发,系统解析了GPU线程调度、内存机制及其在深度学习中的高效计算原理,揭示其为何成为AI芯片首选?

GPU工作原理

·GPU(GraphicsProcessingUnits,GPUs)原是设计用于处理图像视频等数据

·真正让GPU与CPU不同的是

·GPU设计目标是最大化吞吐量(Throughput),比单任务执行快慢,更关心并行度(parallelism),即同时可以执行多少任务

·CPU则更关心延迟(Latency)和并发(concurrency)

·在Z=AX+Y这个示例中,通过并发进行循环展开

·KeepMemorybusbusy,run11659/16=729iterationsatonce

·通过并发使总线处于忙碌的状态当中

·编译器很少对循环展开上100+

·一个线程一次执行上千条指令

·一个线程很难直接处理700个计算负载

·在Z=AX+Y这个示例中,通过并行进行循环展开

·通过并行处理器或多个线程

·同样,KeepMemorybusbusy,run11659/16=729iterationsatonce

·每个线程独立负责相关计算

一共需要729个线程

·程序会受到线程数和内存请求Bound

·并行Parallelism和并发Concurrency

·并行:能够同时处理多个任务

·并发:能够处理多个任务的功能,但不一定是同时

·实际中,更倾向于利用多线程对循环展开,来提高整体硬件的利用率

·GPU特点:有非常非常多的线程,为大量大规模任务并行而去设计

·GPU不是通过增加线程的数量去解决问题,而是去优化线程的执行的速率和效率,这就是CPU与GPU之间最大的区别

·CPU与GPU本质的区别是并行的问题,而不是并发的问题,GPU通过大量的线程提供并行的能力,

·GPUCache缓存机制

·在英伟达A100的架构中,HBMmemory有80G,这80G是显存,是GPU中独立的内存

·这里将一些寄存器文件也当作缓存

·寄存器距离SM(真正的执行单元)非常的近

·片内缓存可能分为多级

·L2Cache,40M,距离显存最近

·L1Cache,192kB

·每个SM都有自己独立的Cache

·Register也是作为Cache里面的一部分,有256kB,一共27MB寄存器

·在A100中,有108个SM

·HBM,高带宽内存,highbandwidthmemory

·GPU线程原理

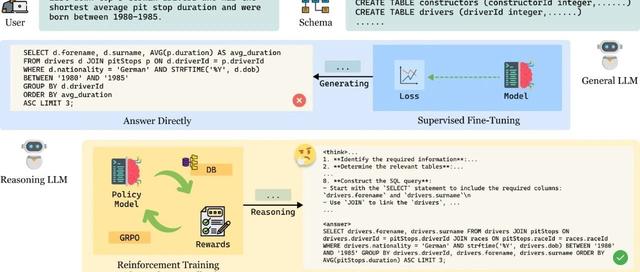

GPUAI编程本质

·思考:为什么GPU适用于AI计算?为什么AI训练使用GPU而不是CPU?

·卷积计算:

·卷积通用过程:图像卷积正常的三通道卷积,输入维度为3维(H,W,3),卷积核维度为(N,C,KH,KW),输出维度为(N,H,W)

·卷积的一般计算方式为:

·Img2col算法过程

·对input进行重排,得到的矩阵见右侧,行数对应输出OHOW个数;每个行向量里,先排列计算一个输出点所需要输入上一个通道的KHKW个数据,再按次序排列之后通道,直到通道IC

·对权重数据进行重排,即以卷积的stride为步长展开后续卷积窗并存在Matrix下一列

·将N个卷积核展开为权重矩阵的一行,因此共有N行,每个行向量上先排列第一个输入通道上KH*KW数据,再依次排列后面的通道直到IC

·卷积操作转换为矩阵相乘,对Kernel和Input进行重新排列

·将输入数据按照卷积窗进行展开并存储在矩阵的列中,多个输入通道的对应的窗展开之后将拼接成最终输出Matrix的一列

·通过数据重排,完成lmg2col的操作之后会得到一个输入矩阵,卷积的Weights也可以转换为一个矩阵,卷积的计算就可以转换为两个矩阵相乘的求解,得到最终的卷积计算结果

·GPU线程分级

·在AI计算模式中,不是所有计算都可以是线程独立的哦

·线程分层执行

·首先有一个图片,第一步用网格Grid对整个图片进行覆盖,切分成一个一个块

·拿出中间一个块进行处理,每一个Grid里面实际上还会分开不同的block,这里的block有可能会重叠

·GPU中的block会去独立的执行

·第三步中,block里面会有大量的线程,通过本地的数据共享(localdatamemory)来去进行计算,每个元素或者每一个像素点,都会给一个线程进行计算

·整个线程是分层分级的

·网格里面的block块,在GPU里面是超额分配的,通过超额分配大量的这些block,而block里面又有大量的线程,每个线程就可以对像素进行大量的操作,而block的超量的分配,就可以通过计算去掩盖延时的问题

·不管是网格也好,线程也好,都会在block里面真正去执行

·并行提升整体计算强度

·并行的能力是最重要的

·并行其实是为了解决带宽慢、带宽时延长的问题

·需要多少线程是由计算复杂度来决定的

·对于Element-wise操作来说,每增加一个线程,就意味着需要对数据进行一次新的加载,因为在GPU里面是并行地去加载,或者并行地去提供线程的,于是增加线程的数量,并不会对实际的运算,或者对实际的时延产生任何的影响,即变成数据的规模在合理的范围内增大并不会影响实际算法的效率,并不会在计算的过程当中,觉得它会变慢了

·由于线程是分级的,同样对于卷积这一类运算的时候,每增加一个线程,对于数据的读取,因为是并行的,它的影响也不会太大,此时,GPU的执行效率与AI的计算模式之间非常匹配

·AI计算模式与线程关系

·矩阵乘MM计算

·卷积的计算可以用矩阵乘来代替

·计算强度与矩阵乘的关系

·算术强度

·GPU硬件架构与CUDA的关系

·NVIDIAA100

·8个GPC(GraphProcessingClusters,图像处理簇)

·每个GPC里面有很多TPC(TextureProcessingClusters,纹理处理簇)

·每个TPC里面有很多SM(StreamMultiprocessors,流多处理器)

·SM里面又有很多Block和Threads

·HBM(HighBandwidthMemory,高带宽存储器)

·包含关系:GPC>TPC>SM>CORE

·SM

·从G80提出的概念,中文称流式多处理器,核心组件包括CUDA核心、共享内存、寄存器等

·SM包含许多为线程执行数学运算的Core,是NVIDIA的核心

·CUDACore:向量运行单元(FP32-FPU、FP64-DPU、INT32-ALU)

·TensorCore:张量运算单元(FP16、BF16、INT8、INT4)

·SpecialFunctionUnits:特殊函数单元SFU(超越函数和数学函数,e.g.反平方根、正余弦等)

·WarpScheduler:线程束调度器(XXThread/clock)

·DispatchUnit:指令分发单元(XXThread/clock)

·MultilevelCache:多级缓存(L0/L1InstructionCache、L1DataCache&SharedMemory)

·RegisterFile:寄存器堆

·Load/Store:访问存储单元LD/ST(负责数据处理)

·在CUDA中的作用:

·可以并发地执行数百个线程

·一个block上线程是放在同一个SM

·一个SM的有限Cache制约了每个block的线程数量

·SP,流处理器(StreamingProcessor)

·最基本的处理单元,也称为CUDACore,最后线程具体的指令和任务都是在SP上处理的

·GPU进行并行计算,也就是很多个SP同时做处理

·SP的消亡:

·Fermi架构后,SP被改称为CUDACore,通过CUDA来控制具体的指令执行

·所以对于现在的N卡架构来说,流处理器数量即CUDACore数量

·所以对于现在的N卡架构来说,流处理器数量即CUDACore数量

·CUDACore,CUDA核

·CUDACore的提出:

·CUDACore在Fermi架构里提出,是最小的运算执行单元

·CUDACore的取消:

··到了Volta架构,CUDACore又和Fermi架构时期发生了变化。从这里开始就没有以前的CUDACore了,而是变成了单独的FP32FPU和INT32ALU

·并行执行:因为FP32:INT32是1:1,所以还是很方便把它们合并成原来的CUDACore去称呼。这样做的好处是每个SM现在支持FP32和INT32的并发执行,更好地提升运算的吞吐量,提升系统的利用率

·Warp,线程束

·逻辑上,所有Thread都是并行的,但是,从硬件的角度来说,并不是所有的Thread能够在同一时刻执行,这里就需要Warp的引入

·即,所有的Thread以锁步的方式执行同一条指令,但每个Thread会使用各自的Data执行指令分支

·如果在Warp中没有32个Thread需要工作,那么Warp虽然还是作为一个整体运行,但这部分Thread是处于非激活状态的

·Thread是最小的逻辑单位,Warp是硬件执行单位

·CUDA基本概念

·ComputeUnifiedDeviceArchitecture

·2006年11月,推出了CUDA,通用并行计算平台和编程模型,用于图形处理单元(GPU)上的通用计算

·并行计算架构(ParallelComputingArchitecture)和编程模型(ProgrammingModel),编程体系

·基于LLVM构建了CUDA编译器,方便开发者使用C进行开发

·提供了对其它编程语言的支持,如C/C++,Python,Fortran等语言

·支持OpenCL和DirectCompute等应用程序接口

·CUDA并行编程模型作为一款通用接口,为熟悉C等标准编程语言的程序员保持较低的学习曲线

·有了这一层,NVIDIA的硬件可以不断去演进,保持软硬件独立解耦,更好地去实现一些硬件的发展

·CUDA在软件方面的组成:

·一个CUDA库、一个应用程序编程接口(API)及其运行库(Runtime)、两个较高级别的通用数学库,即CUFFT和CUBLAS

·CUDA线程层次结构

·主设概念:CUDA引入主机端(host)和设备(device)概念

·CUDA程序中既包含host程序,又包含device程序

·相互通信:host与device之间可以进行通信,这样它们之间可以进行数据拷贝

·CUDA执行流程中最重要的一个过程是调用CUDA的核函数来执行并行计算,kernel是CUDA中一个重要的概念

·在CUDA程序架构中,Host代码部分在CPU上执行,是普通C代码;当遇到数据并行处理的部分,CUDA就会将程序编译成GPU能执行的程序,并传送到GPU,这个程序在CUDA里称作核(Kernel)

·Device代码部分在GPU上执行,此代码部分在kernel上编写(.cu文件)

·kernel用__global__符号声明,在调用时需要用>>来指定kernel要执行的结构

·网格grid

·kernel在device上执行时,实际上是启动了很多线程,一个kernel所启动的所有线程称为一个网格(grid)

·同一个网格上的线程共享相同的全局内存空间

·grid是线程结构的第一层次

·线程块block

·Grid分为多个线程块(block)

·一个block里面包含很多线程

·block间并行执行,并且无法通信,也没有执行

·每个block包含共享内存(SharedMemory),可以里面的Threads共享

·线程thread

·CUDA并行程序,实际上会被多个threads来执行

·多个threads会被组成一个线程block

·同一个block中的threads可以同步,也可以通过sharedmemory通信

·CUDA跟NVIDIA硬件架构的关系

·Block线程块只在一个SM上通过Warp进行调度

·一旦在SM上调起了Block线程块,就会一直保留到执行完kernel

·SM可以同时保存多个Block线程块,块间并行的执行

·Fermi费米架构

·Fermi架构最大可支持16个SMs,每个SM有32个CUDACores,一共512个CUDACores

·整个GPU有多个GPC(图形处理集),单个GPC包含一个光栅引擎(RasterEngine),4个SM

·CUDA线程threads、块blocks和网格grids的层次结构,具有相应的每个线程专用、每个块共享和每个应用程序全局内存空间

·Kepler开普勒架构

·SM改名成了SMX,但是所代表的概念没有大变化

·Kepler架构在硬件上直接有双精运算单元的架构

·提出GPUDirect技术,可以绕过CPU/SystemMemory,完成与本机其他GPU或者其他机器GPU的直接数据交换

·Maxwell麦克斯韦架构

·SM没必要太多,线程数可以超配

·Pascal帕斯卡架构

·SM内部作了进一步精简,整体思路是SM内部包含的东西越来越少,但是总体片上SM数量每一代都在不断增加

·单个SM只有64个FP32CUDACores,相比Maxwell的128和Kepler的192,这个数量要少很多,并且64个CUDACores分为了两个区块

·RegisterFile保持相同大小,每个线程可以使用更多寄存器,单个SM也可以并发更多thread/warp/block

·增加32个FP64CUDACores(DPUnit),FP32CUDACore具备处理FP16的能力

·多机之间,采用InfiniBand和100GbEthernet通信,单机内单GPU到单机8GPU,PCIe带宽成为瓶颈

·NVIDIA提供NVLink用以单机内多GPU内的点到点通信,带宽达到160GB/s,~5倍PCIe3x16

·Volta伏特架构

·CUDACore拆分:分离FPU和ALU,取消CUDACore,一条指令可以同时执行不同计算

·独立线程调度:改进SIMT模型架构,使得每个线程都有独立的PC(ProgramCounter)和Stack

·TensorCore:针对深度学习提供张量计算核心,专门针对卷积计算进行加速

·GRF&Cache:Globalmemory访问也能享受highlybankedcache加速

·SM中包含:

·4个WarpSchedule

·4个DispatchUnit

·64个FP32Core

·64个INT32Core

·32个FP64Core

·8个TensorCore

·32个LD/STUnit

·4个SFU

·FP32和INT32两组运算单元独立出现在流水线中,每个Cycle都可以同时执行FP32和INT32指令

·GPU并行模式实现深度学习功能过于通用,最常见Conv/GEMM操作,依旧要被编码成FMA,硬件层面还是需要把数据按:寄存器-ALU-寄存器-ALU-寄存器,方式来回搬运

·每个TensorCore每周期能执行4x4x4GEMM,即4个FMA(Fused-Multiply-Add,融合乘加运算)。虽然只支持FP16数据,但输出可以是FP32,相当于64个FP32ALU提供算力,能耗上还有优势

·Turing图灵架构

·游戏领域

·两个更新:

·TensorCore

·随着深度学习模型的量化部署渐渐成熟,Turing架构中的TensorCore增加了对INT8/INT4/Binary的支持,为加速deeplearning的Inference

·RTCore(RayTracingCore)光线追踪的核心

·主要用来做三角形与光线的求交,并通过BVH结构加速三角形的遍历

·由于布置在block之外,相对于普通ALU来说是异步

·里面分成两个部分:一部分检测碰撞盒来剔除面片;另一部分做真正的相交测试

·Ampere安培架构

·NVIDIAAmpere架构:超过540亿个晶体管,使其成为世界上最大的7纳米处理器

·TensorCore3.0:新增TF32,包括针对AI的扩展,可使FP32精度的AI性能提高20倍

·Multi-InstanceGPU:多实例GPU,将单个A100GPU划分为多达七个独立GPU,为不同任务提供不同算力

·NVIDIANVLink2.0:GPU间高速连接速度加倍,可在服务器中提供有效的性能扩展

·结构稀疏性:利用了AI数学固有的稀疏特性来使性能提高一倍

·NVIDIAA100基于7nmAmpereGA100GPU,具有6912CUDA内核和432TensorCore,540亿个晶体管数,108个流式多处理器

·采用第三代NVLINK,GPU和服务器双向带宽为4.8TB/s,GPU间的互连速度为600GB/s

·另外,TeslaA100在5120条内存总线上的HBM2内存可达40GB

·Ampere新加入了TF32、BF16、FP64的支持

·每个A100可以被分为7个GPU实例被不同的任务使用,用户可以将这些虚拟的GPU实例当成真实的GPU使用

·为云计算厂商提供算力切分和多用户租赁服务

·8组GPC,66组TPC,132组SM,总计有16896个CUDA核心,528个Tensor核心,50MB二级缓存

·显存为新一代HBM3,容量80G,位宽5120-bit,带宽高达3TB/s

欢迎加入《AI未来星球》,一起成长

扫描下方二维码即可加入~

你可以获得什么?

1、大白之前花费10W+购买,AI行业各场景私有数据集下载,星球内倾情分享;2、AI行业研发、产品、商业落地问题咨询(目前AI公司创业中),都可获高质量解答,有效期一年,无限次提问,有问必答。3、定期邀请AI行业各类嘉宾分享,创业/商业等方面的经验!

帮助你解决遇到的实际问题,升职加薪!

大家一起加油!